Section: New Results

Energy-aware control of systems on chip

Participants : N. Marchand [Contact person] , S. Durand.

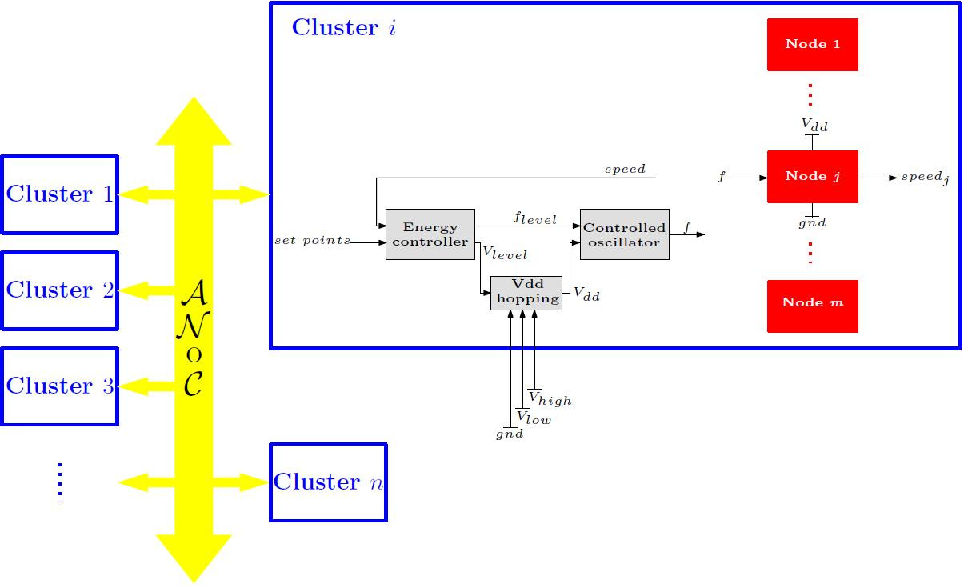

Achieving a good compromise between computing power and energy consumption is one of the challenges in embedded architectures of the future. This management is especially difficult for or known to be at the limit of the scalability, i.e. with a high process variability. This is a key point in the ARAVIS project. Automatic control loops have therefore to be designed to minimize the energy consumption still making the performance fit the requirement in a context of highly technological uncertainties of the chip. This issue is notably discussed in [92] . Finally, the main objective is to dynamically control the computing activity and the energy consumption using the voltage and the frequency according to the requirements of the operating system. In this way, a robust control law was developed in [72] and [32] in order to minimize the high voltage running time with a predictive technique, i.e. to minimize the energy consumption while ensuring good computational performance. This control was initially done for one node (i.e. a processor) but in ARAVIS SoC, the chip is composed of several clusters with several nodes each (see Fig. 9 ). Thus, the energy controller has to manage the voltage level (one voltage domain by cluster) and the frequency for all nodes: a maximal frequency is performed for critical node and then a ratio of this frequency could be apply for the other nodes. Thus, a multicore control strategy with low computational needs was also proposed [71] . This work yields two patents: the first one for the monocore case [70] and the second one for the multicore case [74] .